- Table of Contents

- 1. What does ISO 13485 require from PCB design and manufacturing?

- 2. Why choose microvia and HDI PCBs in medical devices?

- 3. How microvia design choices affect ISO 13485 compliance

- 4. Process validation and traceability for microvia builds

- 5. Testing to prove fitness for intended use

- 6. Documentation you need in your DHF/DMR

- 7. Common pitfalls with microvia PCBs in MedTech (and how to avoid them)

- 8. A practical startup roadmap: from concept to audited production

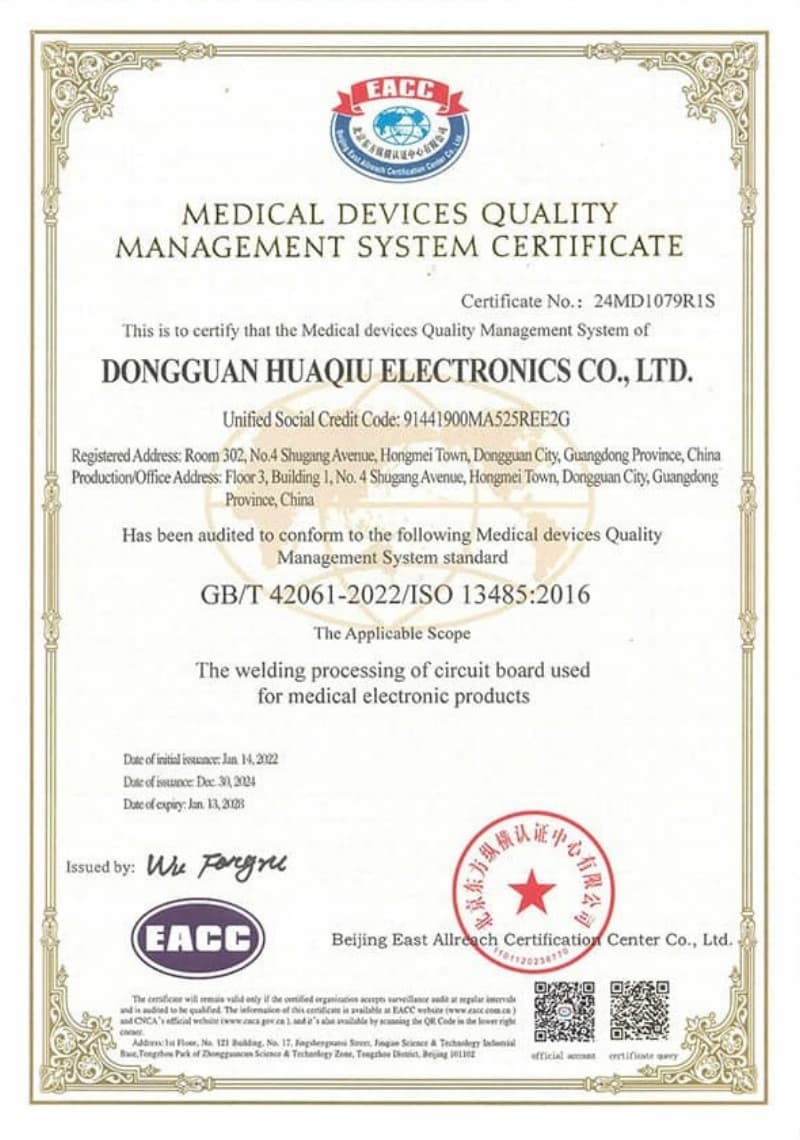

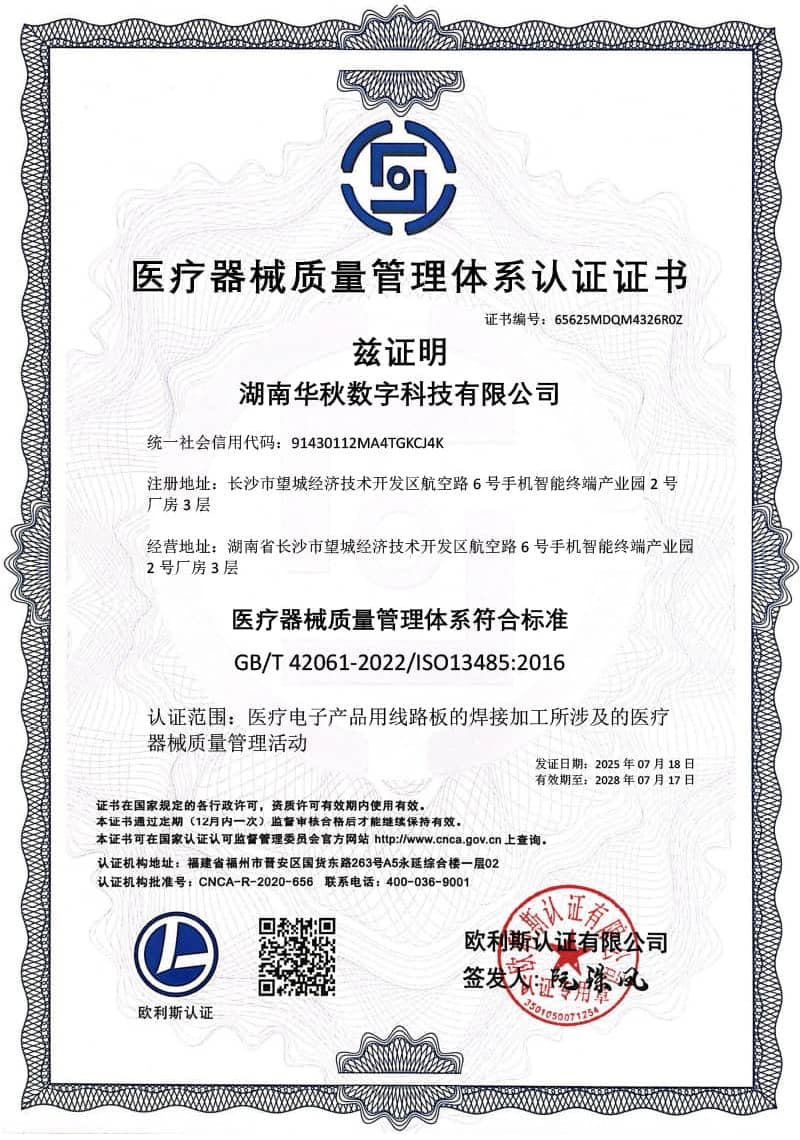

- 9. How NextPCB supports compliant microvia PCB programs

- 10. FAQs

Introduction

Microvia and HDI PCBs make it possible to miniaturize life-saving devices without sacrificing performance. For MedTech startups, the challenge is proving that these advanced interconnects are designed, manufactured, and verified under a quality management system that meets ISO 13485. The good news: by aligning microvia design rules, process validation, and traceability with the standard’s design control and production requirements, you can build evidence of conformity from day one. This guide shows how to connect your PCB decisions to ISO 13485 expectations—covering risk management, material selection, inspection, testing, and documentation—so your team can move from prototype to audited production with confidence.

1. What does ISO 13485 require from PCB design and manufacturing?

ISO 13485 is the medical device quality management standard covering the full lifecycle—design, production, installation, and servicing. It emphasizes risk-based controls, validated processes, and documented evidence of conformity to requirements ISO overview. In 2024, the U.S. FDA finalized the Quality Management System Regulation to align with ISO 13485:2016, reinforcing that medical device makers must embed these practices in everyday engineering and supplier management FDA QMSR aligns with ISO 13485.

For PCB work, the implications are practical:

- Design controls: define design inputs (clinical, electrical, EMC, size), reviews, verification/validation plans, and maintain a design history file.

- Risk management: apply ISO 14971 methods to hazards linked to PCB materials, interconnect reliability, EMI, and manufacturing variability ISO 14971 risk management.

- Process validation: validate special processes where outputs can’t be fully verified by inspection (e.g., laser drilling and copper filling of microvias).

- Traceability: maintain lot-level records linking materials, machines, test results, and personnel; adopt a structured schema such as IPC-1782 for electronics IPC-1782 traceability.

- Evidence of conformity: use recognized standards where possible (IPC-2226 for HDI design; IPC-6012 for rigid PCB performance; IPC J-STD-001 for soldered assemblies and cleanliness) IPC-2226 HDI design standard IPC-6012 IPC J-STD-001.

- Safety and biocompatibility: confirm device-level safety (e.g., IEC 60601-1) and material biocompatibility where relevant (ISO 10993-1) IEC 60601-1 ISO 10993-1.

2. Why choose microvia and HDI PCBs in medical devices?

Microvias are laser-drilled vias typically ≤150 µm in diameter that span a single dielectric layer, enabling high-density interconnect (HDI) stackups. They reduce layer count and routing complexity while supporting fine-pitch BGAs, high-speed signals, and compact form factors.

In MedTech products, microvias help you:

- Fit complex electronics in wearables, implantables, and handheld diagnostics.

- Improve signal integrity and reduce stubs via via-in-pad and short interconnects.

- Enhance power distribution via copper-filled microvias acting as thermal conduits.

- Reduce EMI risk by enabling short return paths and dense ground stitching.

Designing within IPC-2226 guidelines—such as keeping microvia aspect ratio at or below 1:1 and limiting stacked structures—improves manufacturability and long-term reliability IPC-2226 HDI design standard.

3. How microvia design choices affect ISO 13485 compliance

Risk management and design inputs

Tie each microvia choice back to a risk or requirement:

- If your clinical requirement is continuous operation at body temperature with occasional sterilization, define thermal cycle and humidity test limits accordingly.

- If electrical inputs specify 10 Gbps lanes under tight jitter budgets, document via stub length limits, via-in-pad usage, and controlled impedance rules to manage signal integrity risk.

- For shock-prone applications (ambulatory devices), specify copper thickness, pad diameters, and capture annulus that increase mechanical margin.

Map these decisions to identified hazards in your risk file under ISO 14971, with mitigations verified through analysis, inspection, and testing.

Material selection and biocompatibility considerations

- Base materials: Select low-Dk/Df laminates for signal integrity; ensure flammability and safety data support device certification (e.g., UL file listings for materials where required).

- Solder mask and surface finish: Document RoHS/REACH compliance and outgassing/ionic contamination performance for cleanliness-critical devices EU RoHS ECHA REACH.

- Patient-contact risk: If the bare PCB or residues could contact the patient (rare but possible in subassemblies), coordinate with system-level ISO 10993 assessments.

Reliability by design: stacked vs. staggered microvias

Industry data show that stacked microvias are more prone to interfacial cracking at the knee and copper-to-copper interfaces under thermal cycling than staggered structures. The iNEMI position statement recommends preferring staggered microvias or using via-in-pad with copper fill to reduce stress concentration wherever possible iNEMI microvia reliability position statement.

A quick comparison:

- 1. Stacked microvias

- Pros: shortest vertical path; maximal density under fine-pitch BGAs.

- Cons: highest risk of interfacial failures if plating and lamination are not tightly controlled; more demanding process validation.

- 2. Staggered microvias

- Pros: improved reliability through load sharing and stress redistribution; more robust to process variation.

- Cons: slightly larger via fields; more routing complexity.

Supplementary Table 1: Comparison between Stacked and Staggered Microvias

| Microvia Type |

Pros |

Cons |

| Stacked microvias |

Shortest vertical path; maximal density under fine-pitch BGAs. |

Highest risk of interfacial failures if plating and lamination are not tightly controlled; more demanding process validation. |

| Staggered microvias |

Improved reliability through load sharing and stress redistribution; more robust to process variation. |

Slightly larger via fields; more routing complexity. |

When density forces stacking, require copper-filled microvias with proven plating parameters and microsection data to demonstrate integrity across interfaces.

DFM rules that reduce process risk

- Keep microvia aspect ratio ≤1:1 and limit to one dielectric per microvia.

- Use balanced stackups, symmetric copper distribution, and proper resin flow windows.

- Define capture/land sizes and annular rings per IPC-2226; avoid teardrops that mask insufficient registration.

- For via-in-pad, require planarized, copper-filled structures to avoid solder wicking and voids.

- Specify clear acceptance criteria using IPC-6012 Class 3 when device reliability is paramount IPC-6012.

4. Process validation and traceability for microvia builds

Validating laser drilling and copper fill processes

Laser drilling, desmear/cleaning, and copper filling are special processes: you cannot fully verify their quality by end-product inspection alone. Validate them with:

- Installation qualification (IQ): confirm equipment capability (laser pulse width, energy, beam quality; plating rectifiers; agitation/chemistry control).

- Operational qualification (OQ): establish process windows for drill energy, hit count, desmear chemistry, plating current density, and bake cycles; use designed experiments.

- Performance qualification (PQ): run multiple lots over time to show consistent hole quality, fill ratio, and microvia integrity.

Include microsection cross-sections, copper thickness distributions, and void/defect analyses using IPC-TM-650 methods as objective evidence IPC-TM-650 methods.

In-process and final inspection: AOI, X-ray, microsection

- AOI: verify trace/space, pad geometry, solder mask registration, and via target lands.

- X-ray: confirm copper fill, voids, and via-in-pad planarity under dense BGAs.

- Microsection: sample per lot to evaluate wall quality, interfacial bonds, knee geometry, and plating thickness.

Supplementary Table 2: Inspection Methods and Verification Focus

| Inspection Method |

Verification Focus |

| AOI |

Verify trace/space, pad geometry, solder mask registration, and via target lands. |

| X-ray |

Confirm copper fill, voids, and via-in-pad planarity under dense BGAs. |

| Microsection |

Sample per lot to evaluate wall quality, interfacial bonds, knee geometry, and plating thickness. |

Document sampling plans, acceptance criteria, and measurement uncertainty. For cleanliness, align with J-STD-001 process control requirements and retain ionic/solvent extract test data where applicable IPC J-STD-001.

Lot traceability and record keeping

Adopt a traceability schema that links:

- Material lots (laminate, prepreg, chemistries, finishes).

- Machine IDs and process parameters (laser files, plating current/time, bake).

- Operator/training records and maintenance logs.

- In-process and final test results (AOI, X-ray, microsection, electrical test).

Using IPC-1782 levels helps scale the depth of traceability to device risk class and regulatory expectations IPC-1782 traceability.

5. Testing to prove fitness for intended use

Environmental and accelerated life tests

Design verification should reflect the device’s operating environment:

- Thermal cycling to expose interfacial weaknesses in stacked or copper-filled microvias (e.g., −40 to +85/125 °C ranges as appropriate).

- Damp heat and biased HAST for moisture susceptibility.

- Mechanical shock/vibration to evaluate pad cratering and interconnect robustness.

- Sterilization exposure (ETO, gamma, autoclave) if relevant to the product.

Tie test profiles and sample sizes back to identified risks and required confidence levels. Use failure analysis (cross-sections, SEM/EDS) to confirm mechanisms and refine design/process controls.

Electrical tests for safety and performance

- Flying probe or bed-of-nails test for continuity and isolation.

- Impedance coupons for high-speed designs.

- Dielectric withstand/hipot if required by device-level safety standards such as IEC 60601-1 IEC 60601-1.

Retain all raw data, traceable to lot numbers and coupon IDs, in your design history and device master records.

6. Documentation you need in your DHF/DMR

Typical artifacts and evidence

Prepare concise, audit-ready documents:

- Requirements traceability matrix linking design inputs to PCB features.

- Risk management file entries for PCB hazards and mitigations (ISO 14971).

- HDI stackup drawings, via structures, drill charts, and tolerances.

- DFM reviews and supplier capability confirmations.

- Process validation (IQ/OQ/PQ) packages for laser drilling and copper fill.

- Inspection/test plans and results (AOI, X-ray, microsection, electrical).

- Material declarations (RoHS/REACH), flammability ratings, and COC/COA.

- Cleanliness process controls and verification results per J-STD-001.

- Traceability schema and production traveler templates.

Change control and supplier qualifications

- Qualify your PCB manufacturer with audits focused on HDI capability, equipment calibration, chemistry control, and traceability depth.

- Establish change notification thresholds (e.g., laminate brand change, plating chemistry, drill laser model, stackup alterations).

- Maintain an approved vendor list and periodic performance reviews with actionable KPIs (yield, DPPM, on-time delivery, CAPA closure).

7. Common pitfalls with microvia PCBs in MedTech (and how to avoid them)

- Overusing stacked microvias without validating plating parameters—prefer staggered; if stacking is required, mandate copper fill and frequent microsections supported by process capability data iNEMI microvia reliability position statement.

- Pushing aspect ratios beyond 1:1—resize or add layers to preserve plating quality per IPC-2226 IPC-2226 HDI design standard.

- Skipping cleanliness validation in favor of legacy ROSE numbers only—adopt process-based cleanliness controls per J-STD-001 IPC J-STD-001.

- Incomplete traceability—implement IPC-1782 levels that match device risk and regulatory markets IPC-1782 traceability.

- Late material compliance checks—collect RoHS/REACH declarations at sourcing to avoid redesign delays EU RoHS ECHA REACH.

8. A practical startup roadmap: from concept to audited production

- Define design inputs and risks: capture clinical, electrical, EMC, and reliability needs; create a preliminary verification matrix.

- Choose the right HDI strategy: evaluate staggered vs. stacked microvias and via-in-pad based on density, reliability, and assembly risks.

- Engage your PCB partner early: run DFM and stackup feasibility; lock in manufacturable rules.

- Plan validation: draft IQ/OQ/PQ for laser drilling and copper fill; align inspection and test plans with risks.

- Build pilot lots: generate evidence—AOI, X-ray, microsections, electrical and environmental tests—and update the risk file accordingly.

- Freeze the DMR: release controlled drawings, traveler templates, and traceability schemas; formalize change controls.

- Prepare for audits: organize the DHF/DMR; conduct mock audits; ensure supplier records and CAPAs are current.

9. How NextPCB supports compliant microvia PCB programs

As a manufacturing partner experienced in HDI and microvia builds, NextPCB helps startups translate ISO 13485 expectations into practical engineering steps:

- Early-stage DFM and stackup co-design aligned with IPC-2226.

- Controlled laser drilling, desmear, and copper-fill processes, validated with microsection evidence per IPC-TM-650.

- In-line AOI and X-ray for via-in-pad and copper-filled structures, plus electrical test coverage tailored to your risk profile.

- Transparent lot-level traceability, material declarations, and process records that feed directly into your DHF/DMR.

- IPC-class workmanship to the performance requirements you specify (e.g., IPC-6012 Class 2/3), with cleanliness controls per J-STD-001.

Whether you are building first articles or scaling to clinical production, NextPCB provides the documentation trail and technical guidance you need to demonstrate conformity.

>> Explore More PCB Manufacturing & Assembly for Key Industries at NextPCB

10. FAQs

- What makes microvia processes “special” under ISO 13485?

They can’t be fully verified by end inspection; you must validate drilling, desmear, and copper fill with IQ/OQ/PQ and ongoing capability data.

- Are stacked microvias acceptable in medical devices?

Yes, if justified and supported by stringent process validation, copper fill, and reliability testing; staggered microvias are generally more robust.

- Do I need IPC Class 3 for medical PCBs?

Not always; select the class that matches clinical risk and reliability needs, documenting the rationale.

- How do I show traceability for audits?

Implement an IPC-1782 schema linking material lots, process parameters, operators, and test results at the lot level.

- Which tests best reveal microvia weaknesses?

Thermal cycling with periodic microsections and X-ray, supplemented by humidity, shock/vibration, and electrical tests based on risks.

About the Author

Sylvia joined NextPCB two years ago and has already become the go-to partner for clients who need more than just boards. By orchestrating supply-chain resources and refining every step from prototype to mass production, she has repeatedly delivered measurable cost savings and zero-defect launches. Consistency is her hallmark: every client, every order, receives the same uncompromising quality and responsive service.