Support Team

Feedback:

support@nextpcb.comHigh-speed issues including timing and signal integrity (SI) are currently the central issue for digital PCB board designers. Under normal circumstances, the concept of high speed refers to the design of a circuit board with a clock speed of 50MHz or above. According to this definition, 50%-60% of current circuit designs involve high-speed issues. In fact, the importance of high-speed issues is increasing day by day. The following information from Dataquest may prove this point:

Even engineers who simply use the devices on the market today to update "outdated" or "slow" circuit boards will encounter design problems they have never experienced before. Compared with clock speed, high-speed design issues seem to be more closely related to the fast edge speed of the device. Circuit boards are entering a period of high-speed design with a clock speed of only 10MHz.

Many experts agree with this view. Claude Jordon, an experienced authority in the industry, recently said: “All PCB designs will become high-speed designs.” When the speed of individual devices on the circuit board increases, passive interconnections including device packaging will generate parasitics like transmission lines. Effect, which has a negative impact on the performance of the entire system. As an advanced high-speed design, it is necessary to be fully aware of these interrelationships and have the ability to solve these problems.

There is another reason that designers are facing more and more challenges, that is, the gradual increase of key high-speed signal lines on the board. In the past, only 2/5 lines were considered important lines; however, now, this number generally exceeds 50%. For some high-speed applications, the ratio of key traces on each board can reach as much as 90%. At present, there are about 5000 connections on an average board. Today's designers have to deal with everything that high-speed design brings.

In September 1998, among the engineers surveyed by PCB Design Magazine, more than half of the engineers claimed that their designs were 50MHz or above.

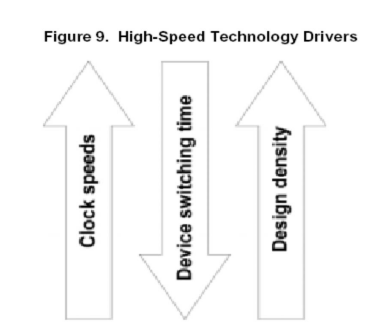

The signal integrity (SI) and timing (timing) issues are a huge wave hitting the field of PCB design, and the timing is quite ripe. The reason can be traced back to three concentrated key factors: the increase of circuit board density, the increase of clock frequency, and the reduction of device switching speed to 0.5ns. The resulting signal integrity problems include increased noise, ringing, and reflections. Furthermore, errors such as excessive gate delay, excessive interconnection delay, clock deviation, and signal instability will increase conversion errors. Circuit boards that suffer from such high-speed effects will give intermittent signs and are often difficult to diagnose. Eventually damage the reliability and even lead to product design failure. This result is obviously unwelcome because it is too expensive.

Although many designers do not fully understand the principles of electrical design, they still need to know how to successfully navigate this dangerous minefield, so as to design high-quality end products according to the plan without exceeding the budget.

Whether it is "rules of thumb" or overly conservative design rules, it has become a yellow flower for the new generation of high-speed design and is no longer applicable. Even many PCB routers now suffer the same fate. In order to successfully face high-speed circuit boards, the router must be able to incorporate a series of external complex design rules, which of course can be automatic or interactive. The crucial high-speed design rules include the following:

Timing aspect:

Signal integrity:

In order to ensure that the actual design always conforms to all predefined constraint rules, the router must be able to perform special processing to automatically turn the signal line. Of course, this function must also be available in the case of interaction; this allows designers to pre-layout key devices and signal lines. In high-speed designs, this approach is generally welcomed. The ideal situation is that all steps are completed in the same comprehensive editing environment, so that the design rules remain unchanged at each stage of the design, from the initial rule definition established by the engineer to the logical design and layout wiring.

The ability to automatically route and adjust differential pairs is particularly important for high-speed designs. It is not a weird thing to encounter a complex and high-performance circuit design containing 1000-2000 differential pairs, especially in the fields of computers, networks and communications. Differential pairs are usually used to reduce the distortion of signals when they are transmitted over long distances and sometimes even between different circuit boards. It is for this reason that a large number of differential pairs are often used in the circuit design of communication stations.

High-speed design usually requires frequent signal analysis and verification, even starting at the schematic production stage. Only by following the design rules and possessing comprehensive analysis tools can the correctness of the final high-speed design be guaranteed. This method can also reduce the number of rework, especially in higher-cost designs in the future.

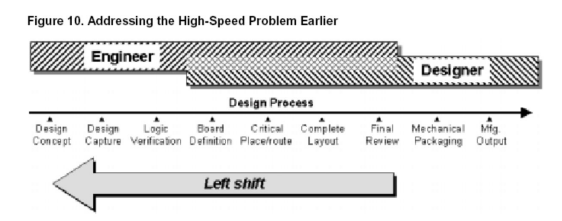

This principle is called "shift left," and it turns out to be surprisingly effective when engineers and designers obtain a comprehensive and comprehensive system. Under the premise of using the same editor, shared rules and design database, the system integrates all the processes involved in the design, from the acquisition of schematic diagrams to various forms of analysis and layout. This saves the designer from having to re-enter the design rules every time and also makes the next stage of simulation easier. Layout analysis is usually performed after the device is placed, so that a more accurate electrical model can be generated, and an analysis is required after wiring. Although the analysis lags behind the entire design process, it will get more accurate results because it can be continuously corrected according to the rules when actually connecting. So far, with the help of crosstalk analysis, all wiring problems can be detected.

In the past, signal integrity analysis did not begin until the layout stage. In order to avoid time-consuming and expensive rework in the future, the analysis must be carried out in advance and continued until the end of the entire design process. Analysis in this way is called "shift left".

The market and technology are fundamentally rapidly and irreversibly affecting PCB design. More and more PCB designers find that routers that can only solve the problems they faced in the past are no longer able to cope with the immediate challenges. The router developed for the next generation design must continue to adhere to higher performance; adapt to the development brought by the latest IC and device packaging; cover high-speed design features; provide interactive and automatic operation functions, of course, the ultimate goal is to be easy to master And use.

Still, need help? Contact Us: support@nextpcb.com

Need a PCB or PCBA quote? Quote now