### KiCad,连接梦想和现实的纽带

KICAD, THE BRIDGE CONNECTING DREAMS

AND REALITY

半糖 HalfSweet

#### Try to create some value

https://github.com/HalfSweet/

halfsweet@halfsweet.cn

https://space.bilibili.com/113604828

@HalfSweet

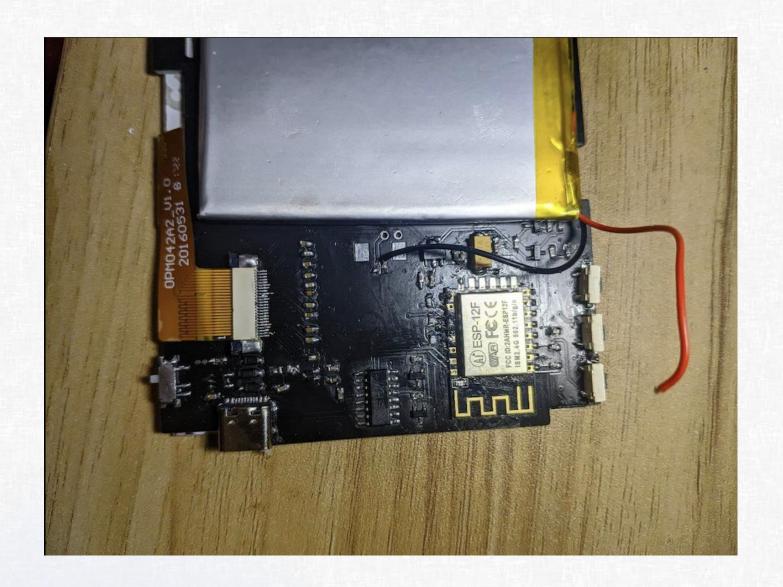

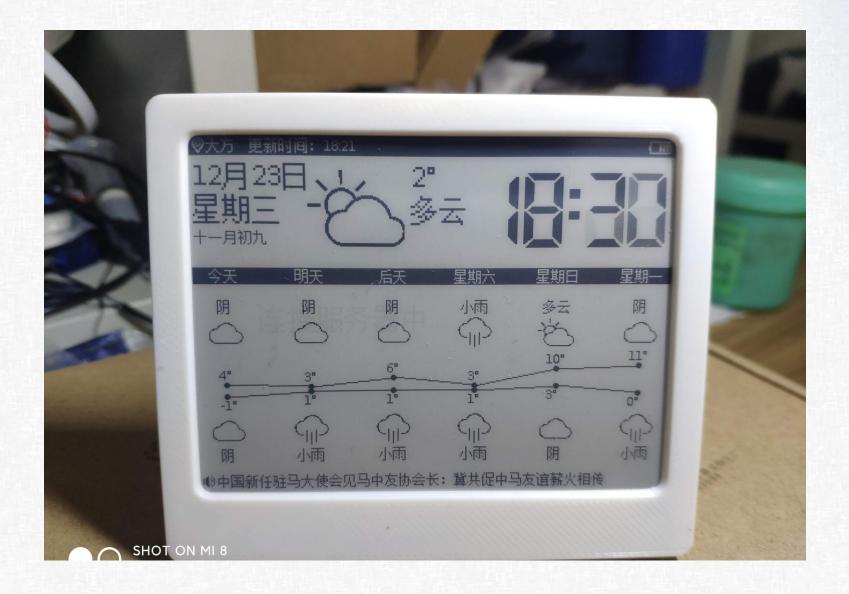

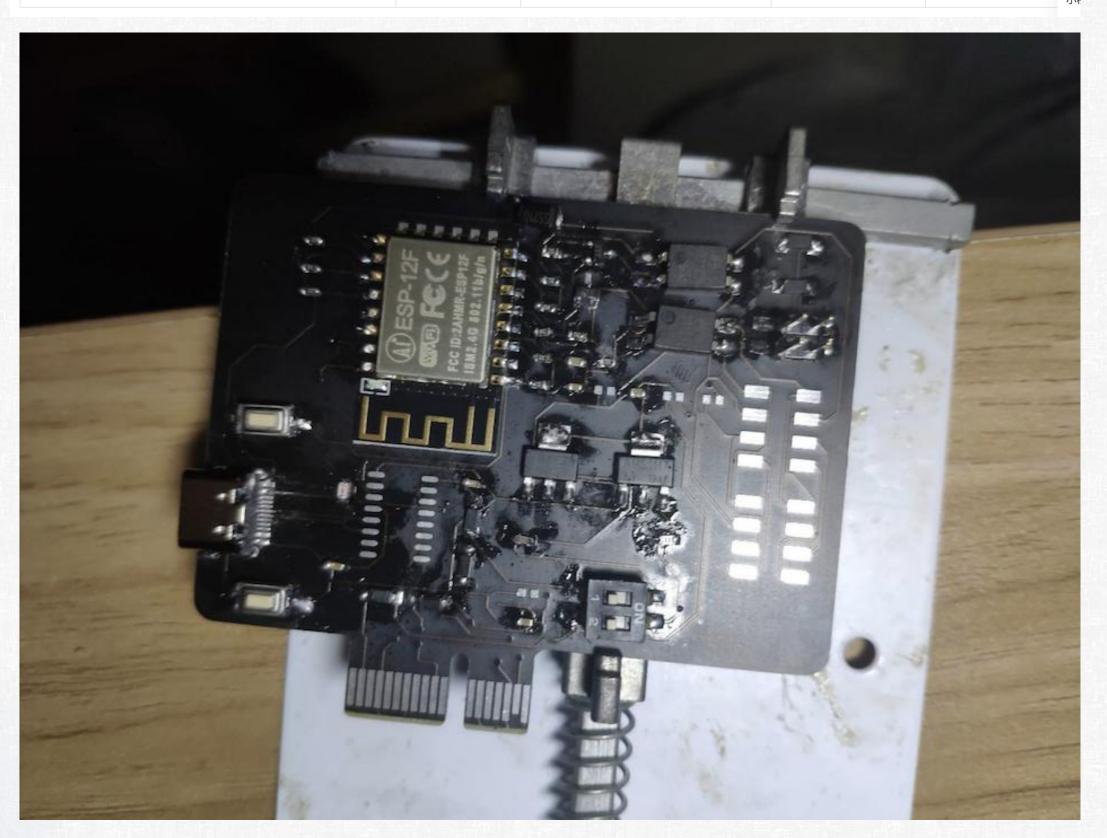

## 我的硬件经历 My Hardware Journey

远程开机

双面板 5片 1.6 哑黑色 有铅喷锡

查看生产稿

已发货 ❷ \_审核结果

进度跟踪

✓ 修改订单

╚上下载工程文件 ⊕ 更多操作

在线支付价

改为需SMT 评价晒单 下激光钢网

<u>订单详情</u>

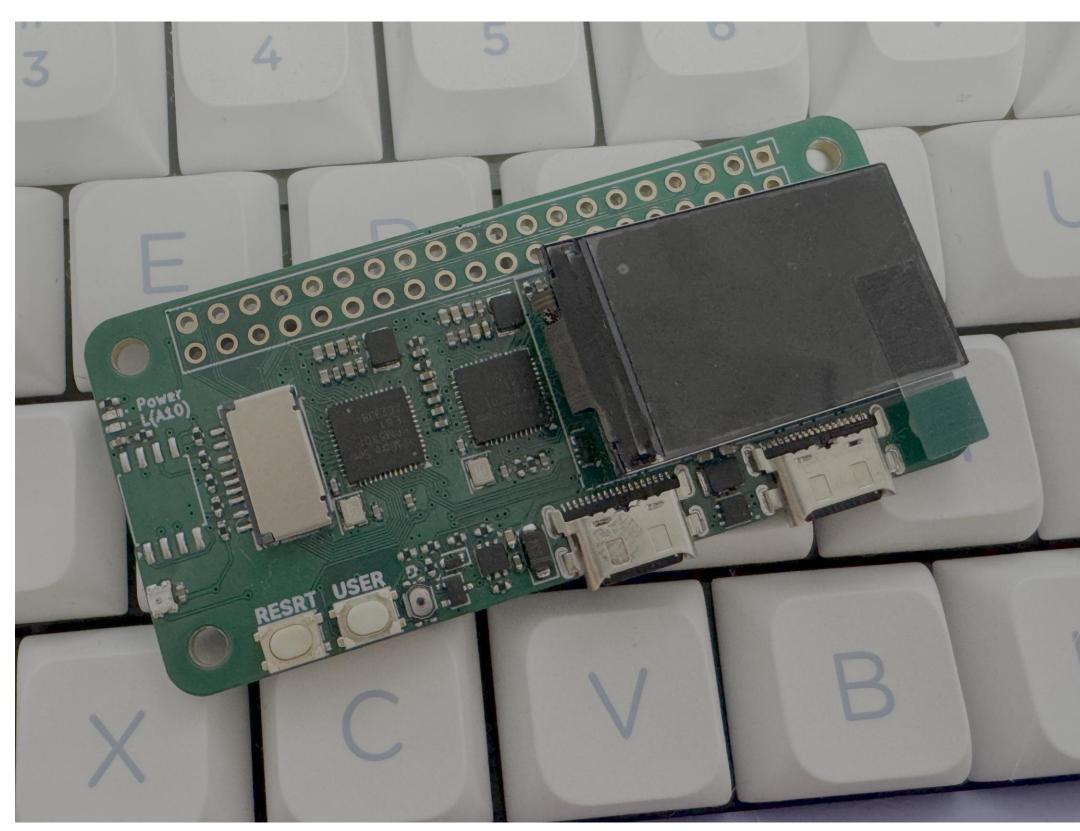

Jlink-OB-RA

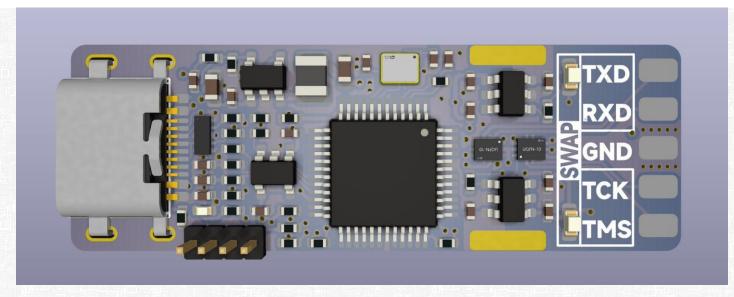

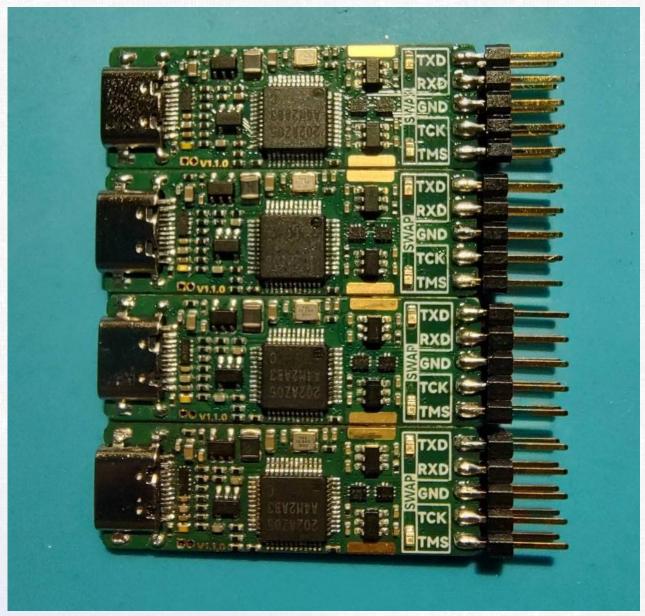

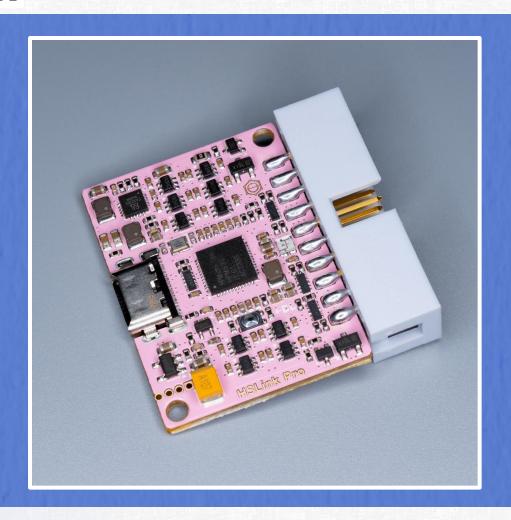

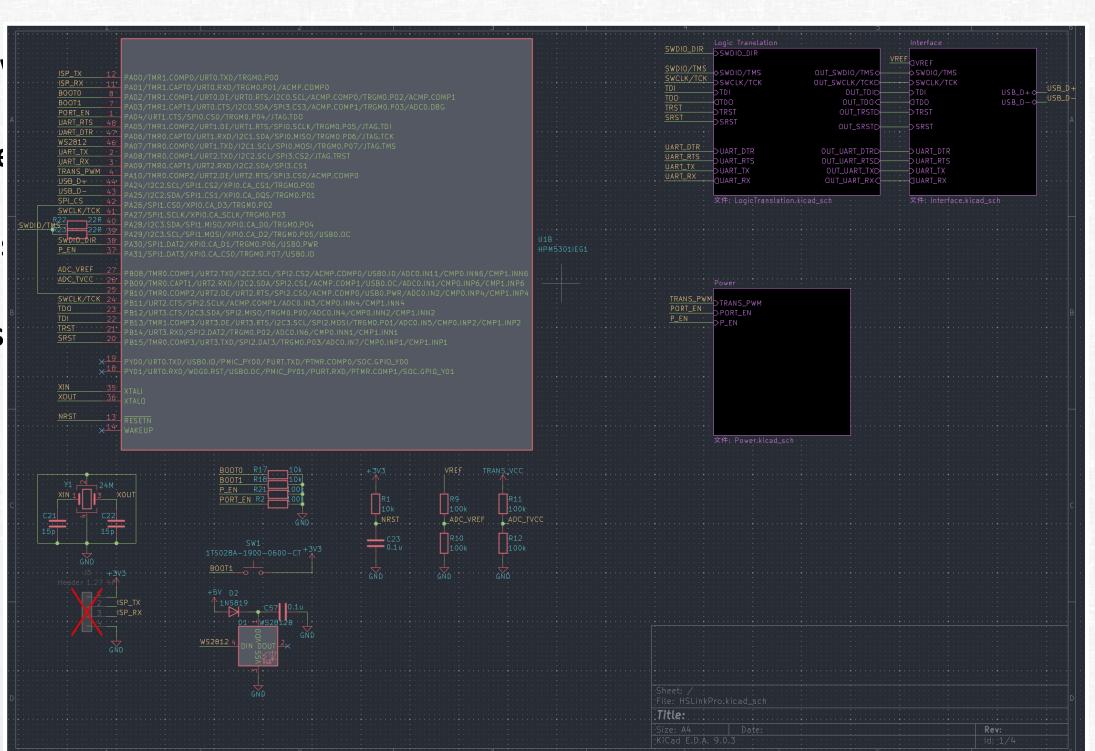

#### **HSLink Pro**

- 80M SWD/JTAG

- 1.8-5V Level support and power output capability, 1A max

- CDC DTR/RTS support

- https://cherrydap.cherryembedded.org/projects/HSLink%20Pro

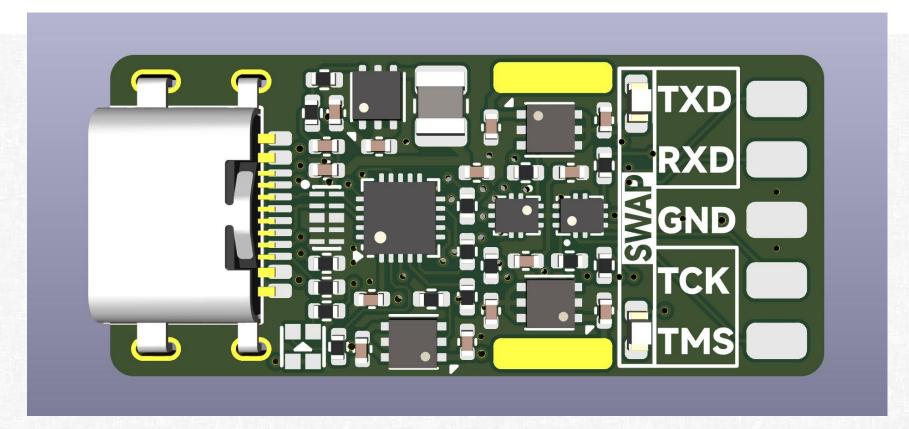

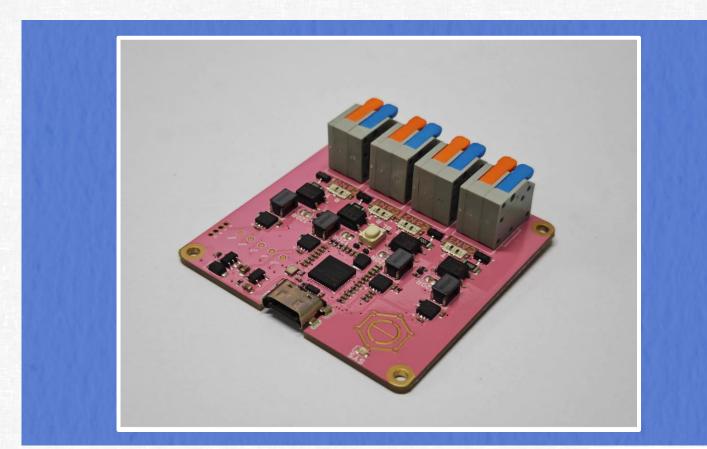

#### **HSCanT**

- 4 channel 8M CAN FD

- Slcan/GS USB support, dynamic switch

- Ecubus Pro

- https://hscant.cherry-embedded.org/

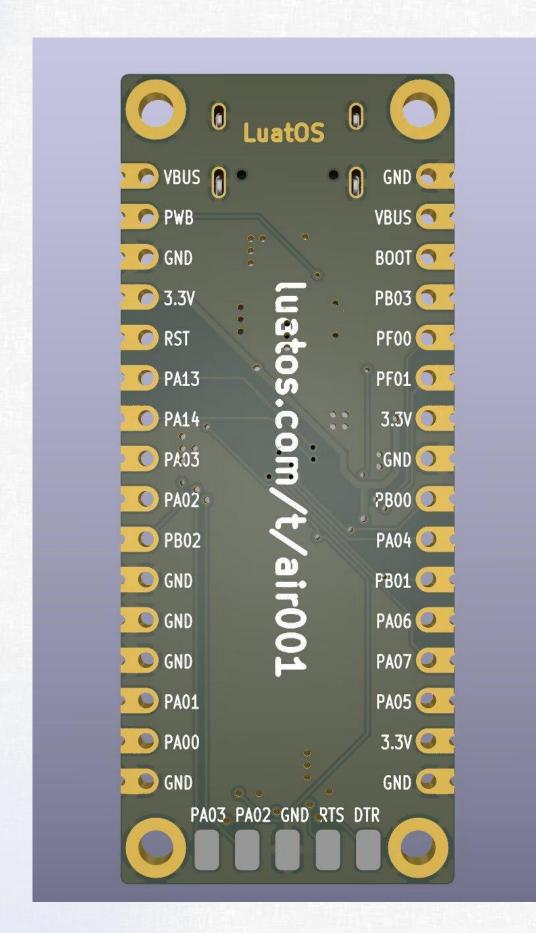

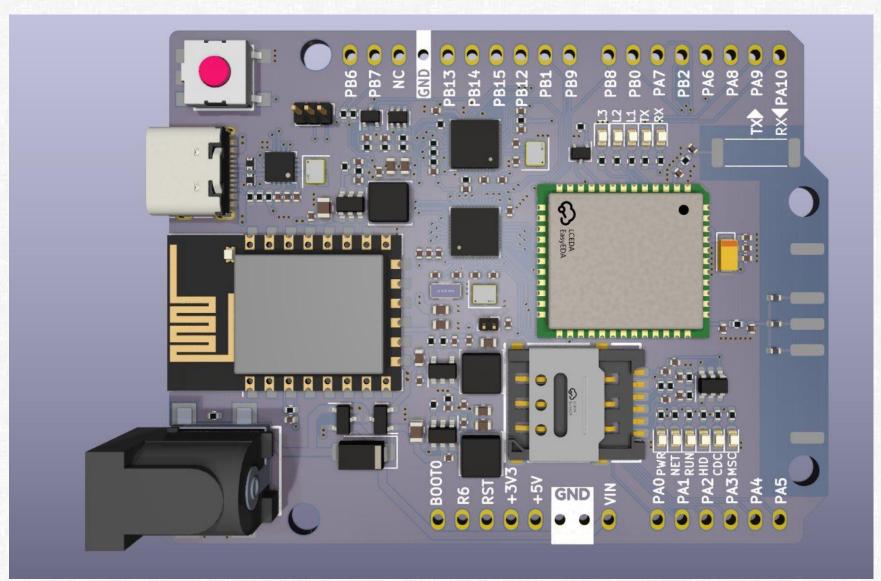

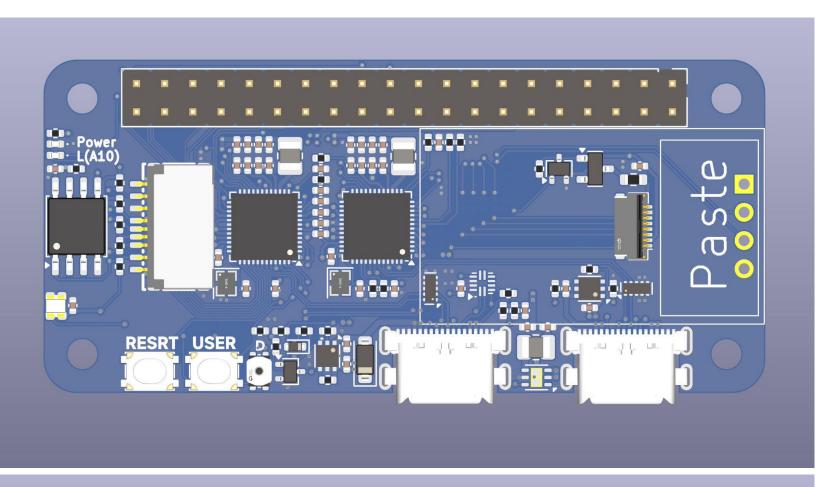

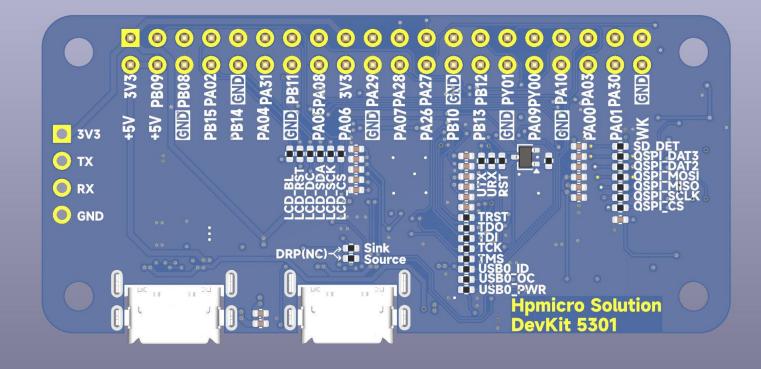

#### HSDevKitS301

#### Why KiCad?

- Native cross-platform support

- Powerful performance that still runs smoothly on lower end devices

- Plain text document format, Git friendly, easy to integrate

- Open Source! A community of freedom, where your copyright always belongs to you

- •I can contribute to the community

- A rich API and plugin system that provides great flexibility and fosters a highly engaged community

- CI/CD-friendly, with kicad-cli and open file formats that facilitate automation.

### Disadvantages of KiCAD?

● The library is still missing many non-standard components; even though the library

maintainers

● Content gene

requirement

MCUs have s

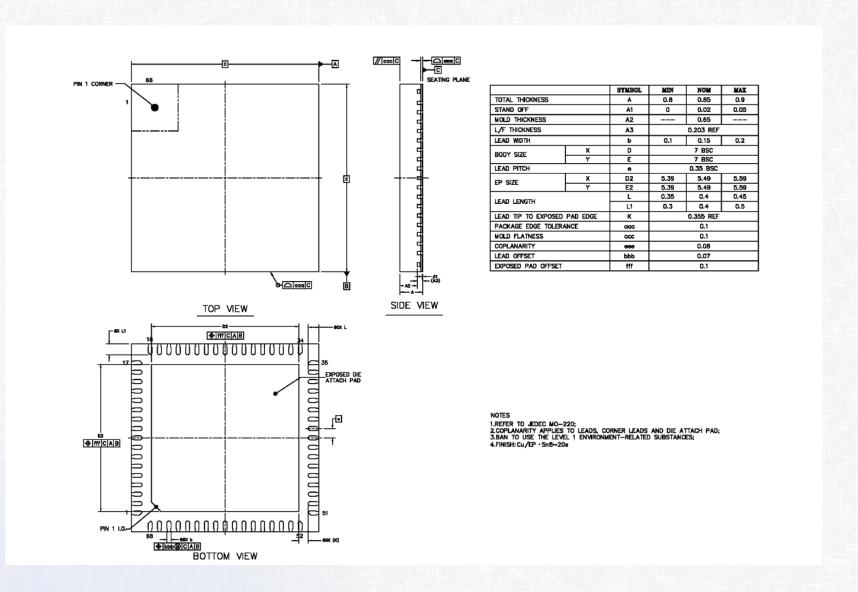

#### Footprint

```

- name: QFN-68-1EP_7x7mm_P0.35mm_EP5.49x5.49mm

size_source: "https://downloads.sifli.com/user%20manual/DS5

device_type: QFN

ipc_class: qfn_pull_back

num_pins_x: 17

num_pins_y: 17

pitch: 0.35

body_size_x:

nominal: 7.0

tolerance: 0.1

body size y:

nominal: 7.0

tolerance: 0.1

overall height:

minimum: 0.85

nominal: 0.9

maximum: 0.95

lead width:

minimum: 0.10

nominal: 0.15

maximum: 0.20

lead_len:

minimum: 0.35

nominal: 0.40

maximum: 0.45

EP size x:

minimum: 5.39

nominal: 5.49

maximum: 5.59

EP_size_y:

minimum: 5.39

nominal: 5.49

maximum: 5.59

EP_num_paste_pads: [3, 3]

thermal_vias:

count: [4, 4]

drill: 0.2

EP_paste_coverage: 0.6

paste_via_clearance: 0.1

```

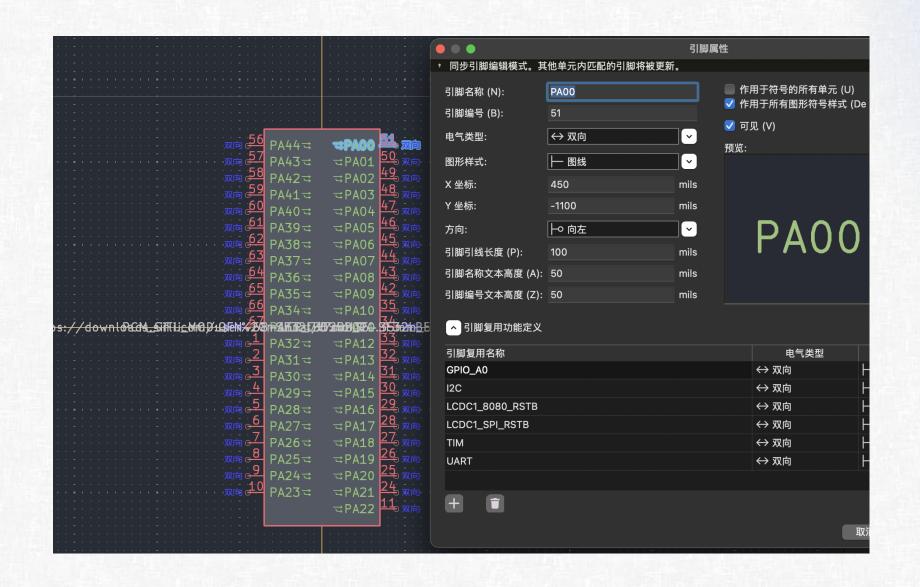

#### Structured Data Built Around the Chip

```

pads:

PA00: &PA00

type: bidirectional

11

pinmux:

12

- {function: GPIO_A0, select: 0}

13

- {function: LCDC1_SPI_RSTB, select: 1}

- {function: I2C, select: 4}

15

- {function: UART, select: 4}

- {function: TIM, select: 5}

17

- {function: LCDC1_8080_RSTB, select: 7}

PA01: &PA01

type: bidirectional

21

- {function: GPIO_A1, select: 0}

- {function: I2C, select: 4}

23

- {function: UART, select: 4}

- {function: TIM, select: 5}

25

PA02: &PA02

type: bidirectional

pinmux:

- {function: GPIO_A2, select: 0}

- {function: LCDC1_SPI_TE, select: 1}

- {function: I2S1_MCLK, select: 3}

- {function: I2C, select: 4}

- {function: UART, select: 4}

- {function: TIM, select: 5}

- {function: LCDC1_JDI_B2, select: 6}

- {function: LCDC1_8080_TE, select: 7}

```

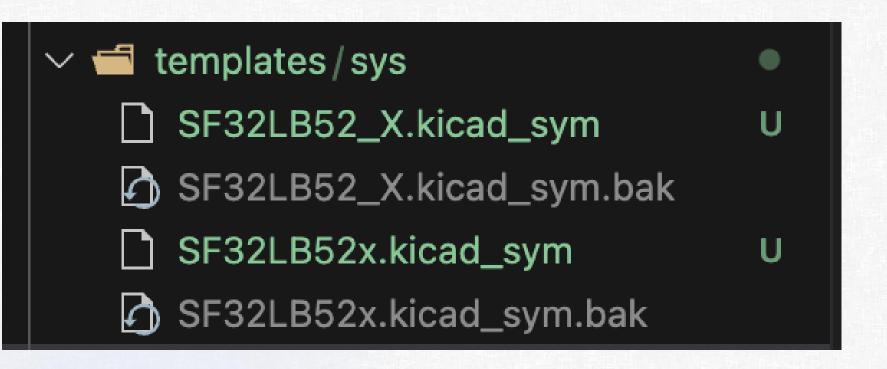

```

variants:

- part_number: SF32LB520U36

description: "8Mb NOR Flash"

package: QFN-68-1EP_7x7mm_P0.35mm_EP5.49x5.49mm

pins: &SF32LB52x QFN68 PINS

504

- {number: 1, pad: *PA32}

- {number: 2, pad: *PA31}

- {number: 3, pad: *PA30}

- {number: 4, pad: *PA29}

- {number: 5, pad: *PA28}

- {number: 6, pad: *PA27}

- {number: 7, pad: *PA26}

- {number: 8, pad: *PA25}

512

- {number: 9, pad: *PA24}

513

- {number: 10, pad: *PA23}

- {number: 11, pad: *PA22}

- {number: 12, pad: *VDD_RTC}

- {number: 13, pad: *VDD_RET}

- {number: 14, pad: *VDD33_VOUT2}

- {number: 15, pad: *VDD_VOUT2}

- {number: 16, pad: *VDD VOUT1}

- {number: 17, pad: *BUCK_FB}

521

- {number: 18, pad: *BUCK LX}

- {number: 19, pad: *VSYS}

- {number: 20, pad: *VBAT}

- {number: 21, pad: *VBUS}

- {number: 22, pad: *VDD33_V0UT1}

- {number: 23, pad: *VDD18_VOUT}

- {number: 24, pad: *VCC}

- {number: 25, pad: *PA20}

```

```

- part_number: SF32LB523UB6

description: "32Mb OPI-pSRAM"

package: QFN-68-1EP_7x7mm_P0.35mm_EP5.49x5.49mm

pins: *SF32LB52x_QFN68_PINS

- part_number: SF32LB525UC6

description: "64Mb OPI-pSRAM"

package: QFN-68-1EP_7x7mm_P0.35mm_EP5.49x5.49mm

pins: *SF32LB52x_QFN68_PINS

- part_number: SF32LB527UD6

description: "128Mb OPI-pSRAM"

package: QFN-68-1EP_7x7mm_P0.35mm_EP5.49x5.49mm

pins: *SF32LB52x_QFN68_PINS

```

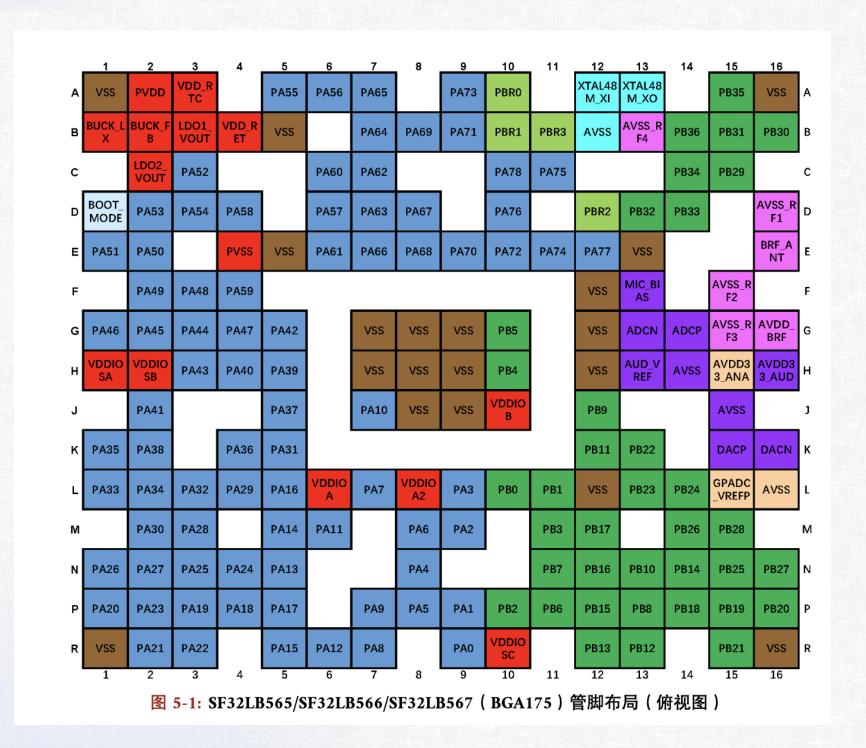

PIN #1 Top View 0.006 Bottom View 0.010 // bbb C DETAIL A TECHNOLOGY SPECIFICATION[技术要求] Side View 1. BALL PAD OPENING: 0. 230mm; [球形防焊开口; 0. 230mm; ] DETAIL A APRIMARY DATUM C AND SEATING PLANE ARE THE SOLDER BALLS; [主要基准C和底面是锡球,] ⚠ DIMENSION 6 IS MEASURED AT THE MAXIMUM SOLDER BALL DIAMETER, PARALLEL TO PRIMARY DATUM C; [尺寸b是测量最大锡球直径,平行于主要基准C;] 4. SPECIAL CHARACTERISTICS C CLASS: bbb, ddd; [特殊特性C类: bbb, ddd; ] ATHE PATTERN OF PIN 1 FIDUCIAL IS FOR REFERENCE ONLY: [PIN 1 标识仅供参考;] 6. BAN TO USE THE LEVEL 1 ENVIRONMENT-RELATED SUBSTANCES; [禁止使用一级环境管理物质;] 图 5-4: BGA175 封装尺寸

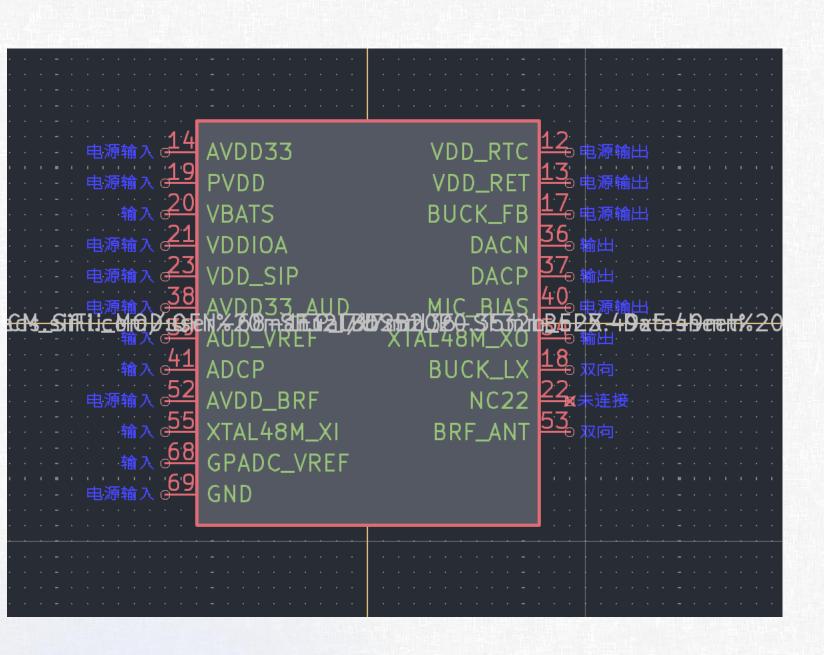

It looks awful! And it's really inconvenient for wiring in the schematic

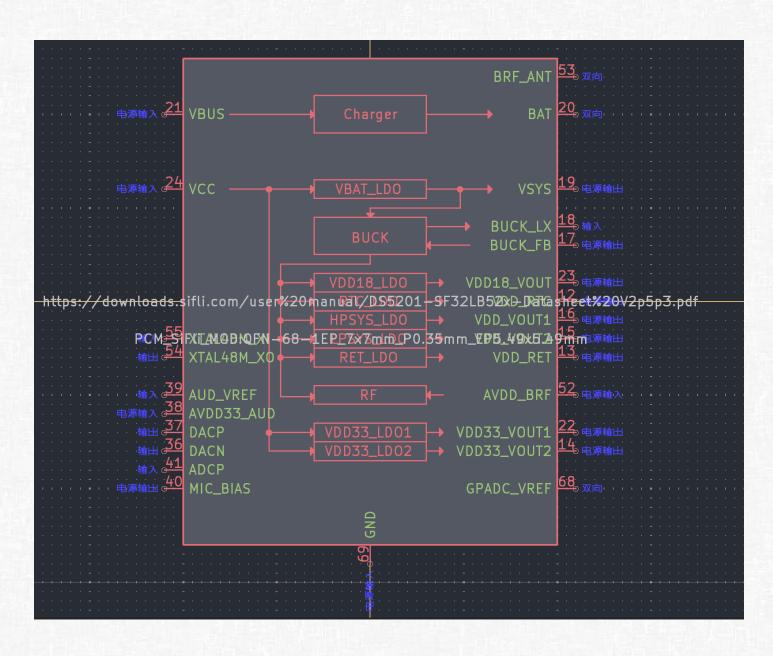

- It is clear that the most complex parts are typically the power supply and analog sections.

- So we can manually edit this part, use it as a template, and replace it during the actual

generation

### Use the plugin system for release

#### Why do we need structured data?

- In the previous workflow, component footprints and symbols were manually created by dedicated engineers lots of repetitive work, heavily manual, and error-prone

- Symbols may be maintained by different people, and different engineers have different tastes, so the visual style is inconsistent

- There is no effective version control mechanism, so updates are hard to propagate to every endpoint

- Software and hardware are like isolated islands, and we still have to synchronize them manually.

- The existing workflow does not adhere well to the DRY (Don't Repeat Yourself) principle

#### Bridging hardware and software

- We can leverage KiCad's plugin system to import and export alternate functions

- The alternate functions table can act as a common initialization source for various software, such as sifli-rs and Zephyr device tree

- By performing checks in the automation flow in advance, we can eliminate potential errors before actual production

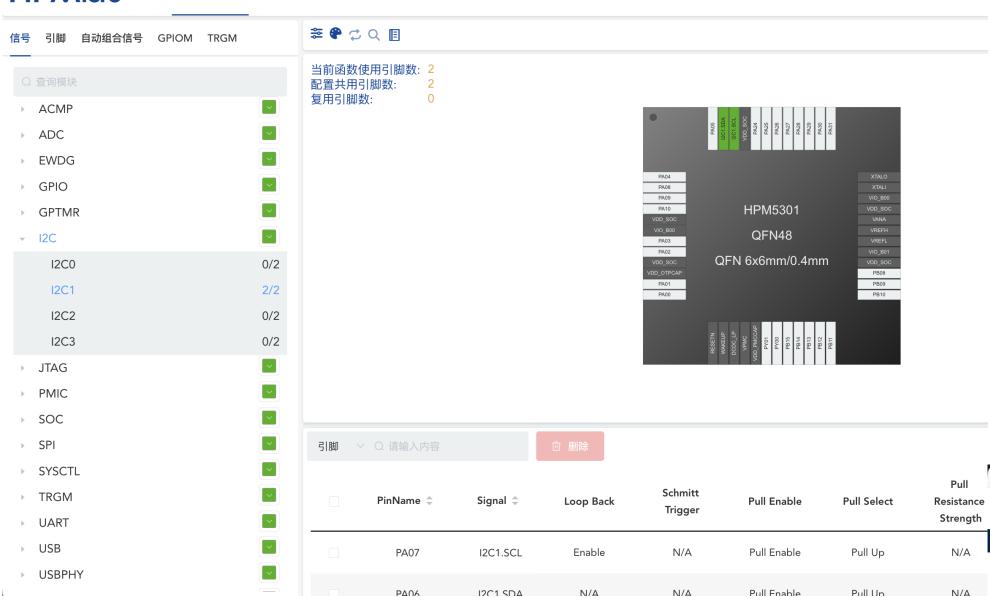

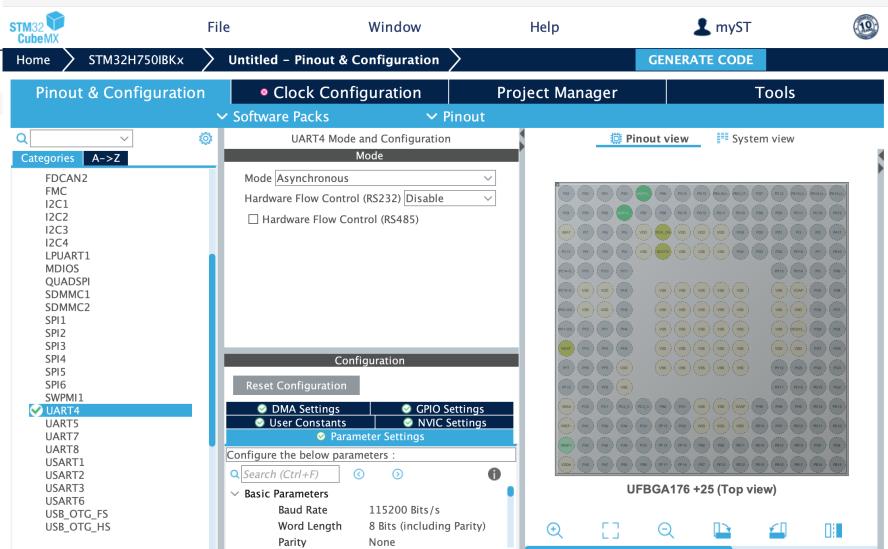

- Structured data can also be used as a data source for external tools, for example tools similar to STM32CubeMX or HPMicro Tools

HPM5301\_QF

STM32CubeMX Untitled\*: STM32H750IBKx

# 谢谢

THANKS